# **1.5A Dual WLED Flash Driver** with I<sup>2</sup>C Compatible Interface

#### DESCRIPTION

The EUP2471 is a 2MHz fixed frequency, current mode synchronous boost converter. The device is designed to operate as a dual 750mA (1.5A total) constant current driver for flash white LED application.

An industry-standard  $I^2C$  serial digital input is used to enable, disable and set the movie-mode current for each flash LED with up to 16 movie-mode settings. The EUP2471 also includes a separate Flash Enable input to initiate both the flash operation and the default timer, which can be used either to terminate a flash event at the end of a user-programmed delay or as a safety feature. The maximum flash and movie-mode current is set by one external resistor; the ratio of Flash to Movie-mode current is set at approximately 6.1:1.

An over-voltage protection feature keeps the output voltage below the OVP threshold in case of an open LED and an output short circuit protection limits the output current during an output short to GND. The chip's quiescent current is less than  $1.0\mu$ A in shutdown mode.

#### FEATUES

• 2.7V to 5.5V Input Supply Range

「」」「」四海恒通科技 www.gofotech.com

Tel: 0755-8398 3377 0755-8301 8377 企业QQ: 23556 33399

EUP2471

- Dual Channel Output with Separate Flash Enable

- Up to 1.5A Regulated Output Current (750mA per channel)

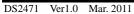

- Up to 85% Efficiency

- 2 MHz Fixed Switching Frequency

- I<sup>2</sup>C Compliant Serial Interface

400kHz Serial Transfer Rate

16 Level Movie-mode Current

Flash/Movie-mode

- -Programmable LED Current

- -Programmable Flash Safety Timer

- True Load Disconnect

- Input Current Limit

- Output Over-Voltage, Short Circuit, and Over-Temperature Protection

- 3mm×3mm TDFN-14 Package

- RoHS Compliant and 100% Lead (Pb)-Free Halogen-Free

#### **APPLICATIONS**

- Camera-enabled Cellular Phones and Smart Phones

- Digital Still Cameras (DSCs)

- LED Photo Flash/Torch

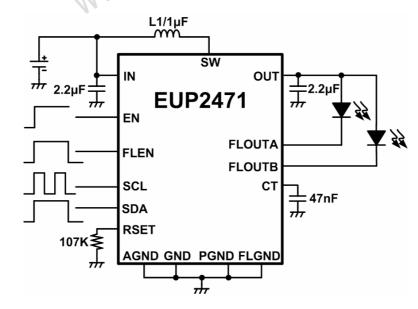

Figure 1. EUP2471 Typical Application

# **Typical Application Circuit**

| Package Type | Pin Configurations                           |  |             |                                                   |                 |

|--------------|----------------------------------------------|--|-------------|---------------------------------------------------|-----------------|

|              |                                              |  | (TOP VIEW)  |                                                   |                 |

| TDFN-14      | CT<br>EN<br>FLEN<br>AGND<br>IN<br>SW<br>PGND |  | Thermal Pad | 14)<br>(13)<br>(12)<br>(11)<br>(10)<br>(9)<br>(8) | FLOUTA<br>FLGND |

|              |                                              |  |             |                                                   | J               |

# **Pin Configurations**

# **Pin Description**

| r III Desci    | -       |                                                                                                                                                                                                                                                                                             |

|----------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN            | TDFN-14 | DESCRIPTION                                                                                                                                                                                                                                                                                 |

| 1 CT           |         | Flash timer control input. Connect a capacitor between CT and AGND to set maximum                                                                                                                                                                                                           |

|                |         | duration of the flash pulse. To disable the flash timer, connect CT to AGND.                                                                                                                                                                                                                |

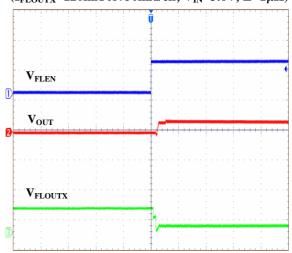

| 2              | EN      | Enable input. EN is an active HIGH asserted input. EN must be strobed low-to-high to enable the EUP2471 to accept I <sup>2</sup> C programming instructions.                                                                                                                                |

| 3              | FLEN    | Flash enable pin. A low-to-high transition on the FLEN pin initiates a flash pulse and starts the flash timer.                                                                                                                                                                              |

| 4              | AGND    | Analog ground pin. Connect AGND to PGND, GND, and FLGND at a single point as close to the EUP2471 as possible.                                                                                                                                                                              |

| 5              | IN      | Power input. Connect IN to the input power supply voltage. Connect a 2.2µF or larger ceramic capacitor from IN to PGND as close as possible to the EUP2471.                                                                                                                                 |

| 6              | SW      | Boost converter switching node. Connect a 1µH inductor between SW and IN.                                                                                                                                                                                                                   |

| 7              | PGND    | Power ground pin. Connect PGND to AGND, GND, and FLGND at a single point as close to the EUP2471 as possible.                                                                                                                                                                               |

| 8              | OUT     | Power output of the boost converter. Connect a $2.2\mu$ F or larger ceramic capacitor from OUT to PGND as close as possible to the EUP2471. Connect OUT to the anode(s) of the Flash LED(s).                                                                                                |

| 9              | SCL     | I <sup>2</sup> C interface serial control line.                                                                                                                                                                                                                                             |

| 10             | SDA     | I <sup>2</sup> C interface serial data/address.                                                                                                                                                                                                                                             |

| 11             | FLOUTB  | Flash Output B. Connect cathode of Flash LEDB to FLOUTB. For a single flash LED, connect FLOUTB and FLOUTA together. For two flash LEDs, each output will conduct 50% of the total flash output current.                                                                                    |

| 12             | FLGND   | Flash ground pin. Connect FLGND to PGND, GND, and AGND at a single point as close to the EUP2471 as possible.                                                                                                                                                                               |

| 13             | FLOUTA  | Flash Output A. Connect cathode of Flash LEDA to FLOUTA. For a single flash LED, connect FLOUTA and FLOUTB together. For two flash LEDs, each output will conduct 50% of the total flash output current.                                                                                    |

| 14             | RSET    | Flash current setting input. A $107k\Omega$ resistor from RSET to AGND sets the maximum flash current available at FLOUTA and FLOUTB to 1.5A. Each FLOUTA and FLOUTB channel will conduct 50% of the maximum programmed current. The EUP2471's flash-to-movie-mode ratio is fixed at 6.1:1. |

| Thermal<br>Pad | -       | Thermal paddle (bottom); Connect EP to PGND as close as possible to the EUP2471.                                                                                                                                                                                                            |

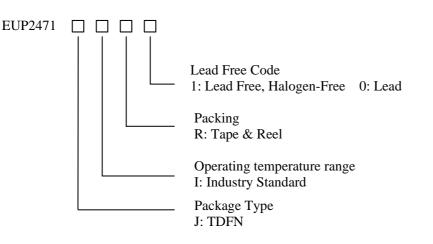

#### **Ordering Information**

| Order Number | Package Type | Marking        | <b>Operating Temperature Range</b> |

|--------------|--------------|----------------|------------------------------------|

| EUP2471JIR1  | TDFN-14      | xxxxx<br>P2471 | -40 °C to +85°C                    |

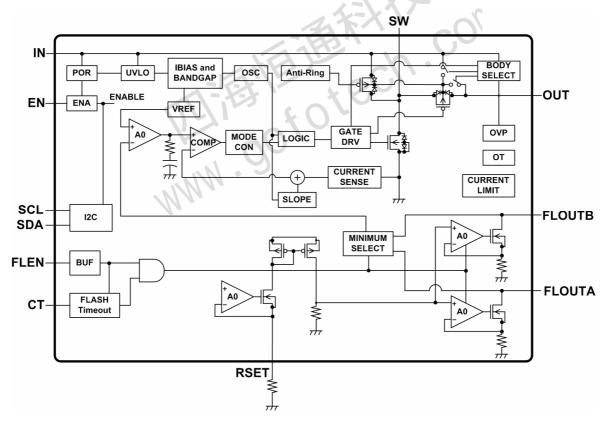

**Block Diagram**

#### **Absolute Maximum Ratings**

| 6                                                                     |

|-----------------------------------------------------------------------|

| • IN, SW, OUT0.3V to 6V                                               |

| ${\scriptstyle \bullet}$ RSET, EN, FLEN, SDA, SCL, CT, FLOUTA, FLOUTB |

| <ul> <li>Power Dissipation, PD@ T<sub>A</sub>=25°C</li> </ul>         |

| TDFN-14 1.923W                                                        |

| <ul> <li>Package Thermal Resistance</li> </ul>                        |

| θ <sub>JA</sub> (TDFN-14) 65°C/W                                      |

| Junction Temperature Range                                            |

| • Lead Temperature (Soldering, 10sec.) 260°C                          |

| • Storage Temperature Range65°C to 150°C                              |

|                                                                       |

# **Recommended Operating Conditions**

|                                                | Min | Max | Unit |

|------------------------------------------------|-----|-----|------|

| Supply voltage, V <sub>IN</sub>                | 2.6 | 5   | V    |

| Operating free-air temperature, T <sub>A</sub> | -40 | 85  | °C   |

# **Electrical Characteristics**

$V_{IN} = 3.6V$ ,  $C_{IN} = 2.2\mu$ F,  $C_{OUT} = 2.2\mu$ F,  $L = 1\mu$ H,  $R_{SET} = 107$ k $\Omega$ ,  $T_A = -40^{\circ}$ C to  $85^{\circ}$ C, unless otherwise noted. Typical values are at  $T_A = 25^{\circ}$ C.

| Symbol                   | Devenuetor                            |                                                                              | EUP2471 |      |      | T       |

|--------------------------|---------------------------------------|------------------------------------------------------------------------------|---------|------|------|---------|

| Symbol                   | Parameter                             | Conditions                                                                   | Min.    | Тур. | Max. | Unit    |

| Power Supply             |                                       |                                                                              | )       |      |      | <u></u> |

| V <sub>IN</sub>          | Input Voltage Range                   | 1212                                                                         | 2.7     |      | 5.5  | V       |

| V <sub>OUT(MAX)</sub>    | Maximum Voltage                       |                                                                              |         |      | 5.5  | V       |

| т                        | Summly Current                        | Flash Mode, I <sub>LOAD</sub> =1.5A                                          |         | 0.48 |      | mA      |

| I <sub>IN(Q)</sub>       | Supply Current                        | Movie Mode                                                                   |         | 0.45 |      | mA      |

| I <sub>SHUTDOWN</sub>    | V <sub>IN</sub> Shutdown Current      | EN=FLEN=GND                                                                  |         |      | 1    | μΑ      |

| I <sub>FL(TOTAL)</sub>   | Total Output Current, Flash Mode      | R <sub>set</sub> =107kΩ,<br>FLOUTA + FLOUTB                                  |         | 1.5  |      | А       |

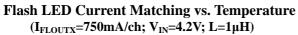

| I <sub>FL(MATCH)</sub>   | FLOUTA and FLOUTB Current<br>Matching |                                                                              |         | 10   |      | %       |

| I <sub>MM(LOAD)</sub>    | Total Output, Movie Mode              | $R_{SET}$ =107k $\Omega$ , Movie Mode Current<br>Set = 100%; FLOUTA + FLOUTB |         | 220  |      | mA      |

| Fosc                     | Switching Frequency                   | $T_A=25^{\circ}C$                                                            |         | 2.0  |      | MHz     |

| t <sub>DEFAULT</sub>     | Default On Time                       | C <sub>T</sub> =74nF                                                         |         | 600  |      | ms      |

| T <sub>SD</sub>          | Thermal Shutdown Threshold            |                                                                              |         | 140  |      | °C      |

| T <sub>SD(HYS)</sub>     | Thermal Shutdown Hysteresis           |                                                                              |         | 15   |      | °C      |

| I <sup>2</sup> C Control | I – SDA, SCL                          |                                                                              |         |      |      |         |

| V <sub>IL</sub>          | Input Threshold Low                   |                                                                              |         |      | 0.4  | V       |

| V <sub>IH</sub>          | Input Threshold High                  |                                                                              | 1.4     |      |      | V       |

| II                       | Input Current                         |                                                                              | -1.0    |      | 1.0  | μΑ      |

| V <sub>OL</sub>          | Output Logic Low (SDA)                | I <sub>PULLUP</sub> =3mA                                                     |         |      | 0.4  | V       |

| f <sub>SCL</sub>         | SCL Clock Frequency                   |                                                                              | 0       |      | 400  | kHz     |

| t <sub>LOW</sub>         | SCL Clock Low Period                  |                                                                              | 1.3     |      |      | μs      |

| t <sub>HIGH</sub>        | SCL Clock High Period                 |                                                                              | 0.6     |      |      | μs      |

| t <sub>HD_STA</sub>      | Hold Time START Condition             |                                                                              | 0.6     |      |      | μs      |

| t <sub>SU_STA</sub>      | Setup Time for Repeat START           |                                                                              | 0.6     |      |      | μs      |

# **Electrical Characteristics (Continued)**

$V_{IN} = 3.6V$ ,  $C_{IN} = 2.2\mu$ F,  $C_{OUT} = 2.2\mu$ F,  $L = 1\mu$ H,  $R_{SET} = 107$ k $\Omega$ ,  $T_A = -40^{\circ}$ C to 85°C, unless otherwise noted. Typical values are at  $T_A = 25^{\circ}$ C.

| Symbol                                       | Parameter                                         | Conditions | F    | EUP2471 |      |      |

|----------------------------------------------|---------------------------------------------------|------------|------|---------|------|------|

| Symbol                                       | rarameter                                         | Conditions | Min. | Тур.    | Max. | Unit |

| I <sup>2</sup> C Control                     | I <sup>2</sup> C Control – SDA, SCL               |            |      |         |      |      |

| t <sub>SU_DAT</sub>                          | SDA Data Setup Time                               |            | 100  |         |      | ns   |

| t <sub>HD_DAT</sub>                          | SDA Data Hold Time                                |            |      |         | 0.9  | μs   |

| t <sub>SU_STO</sub>                          | Setup Time for STOP Condition                     |            | 0.6  |         |      | μs   |

| t <sub>BUF</sub>                             | Bus Free Time between STOP and<br>START Condition |            | 1.3  |         |      | μs   |

| EN, FLEN                                     | EN, FLEN Logic Control                            |            |      |         |      |      |

| V <sub>EN(L)</sub> ,<br>V <sub>FLEN(L)</sub> | EN, FLEN Input Low Threshold                      |            |      |         | 0.4  | v    |

| V <sub>EN(H)</sub> ,<br>V <sub>FLEN(H)</sub> | EN, FLEN Input High Threshold                     |            | 1.4  |         |      | v    |

| t <sub>FLEN_OND</sub>                        | FLEN ON Delay Time                                | EN= AGND   |      | 80      |      | μs   |

| t <sub>FLEN_OFFD</sub>                       | FLEN OFF Delay Time                               | EN= AGND   |      | 2       |      | μs   |

THIS COR WWW.9010tech.

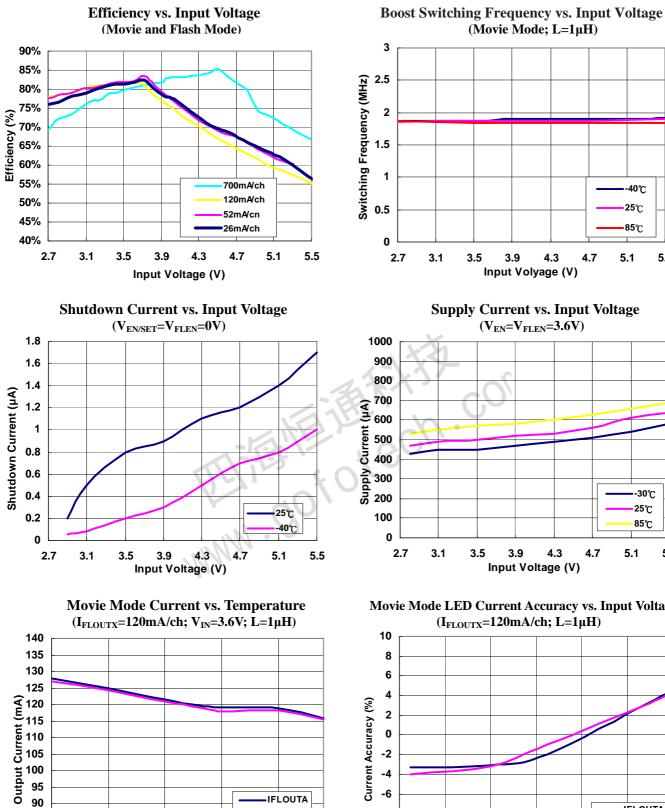

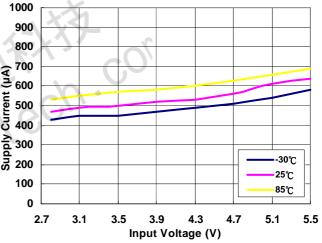

# **Typical Operating Characteristics**

(Movie Mode; L=1µH) -**40℃ 25℃ 85℃** 3.5 3.9 4.3 5.1 5.5 4.7 Input Volyage (V)

EUP2471

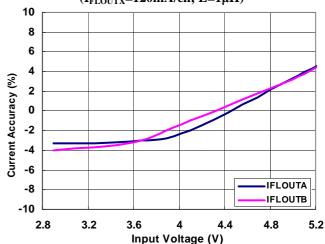

Supply Current vs. Input Voltage  $(V_{EN}=V_{FLEN}=3.6V)$

Movie Mode LED Current Accuracy vs. Input Voltage (I<sub>FLOUTX</sub>=120mA/ch; L=1µH)

-15

10

Temperature (℃)

35

85

80

-40

IFLOUTA

IFLOUTB

60

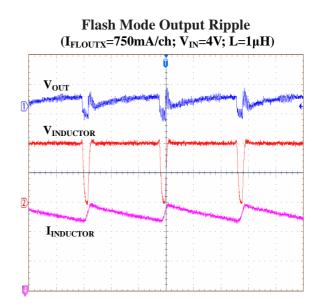

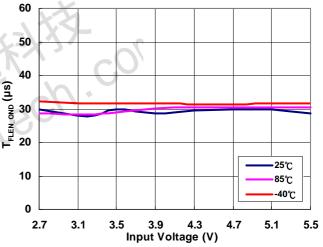

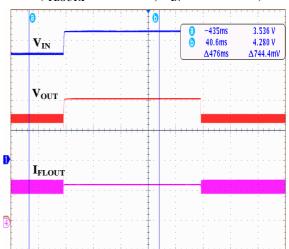

# **Typical Operating Characteristics (Continued)**

EUP2471

Flash On Time Delay vs. Input Voltage (I<sub>FLOUTX</sub>=750mA/ch; C<sub>OUT</sub>=2.2µF; L=1µH)

Movie Mode Line Transient (I<sub>FLOUTX</sub>=120mA/Ch; V<sub>IN</sub>=4.2V to 3.6V)

# Typical Operating Characteristics (Continued)

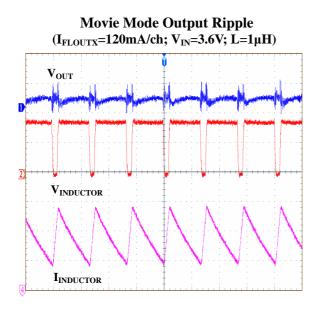

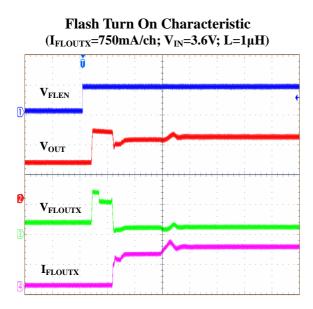

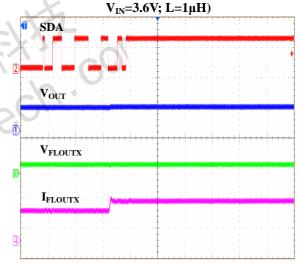

Movie Mode Turn On Characteristic (I<sub>FLOUTX</sub>=120mA/ch; V<sub>IN</sub>=3.6V; L=1µH)

Movie Mode to Flash Turn On Characteristic (I<sub>FLOUTX</sub>=120mA to750mA/ch; V<sub>IN</sub>=3.6V; L=1µH)

EUP2471

Movie Mode Transient Characteristic (I<sub>FLOUTX</sub>=102mA to 188mA/ch; C<sub>OUT</sub>=0.22µF;

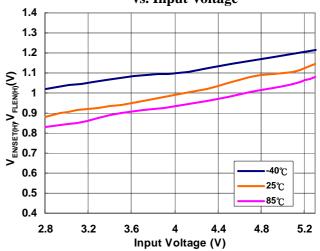

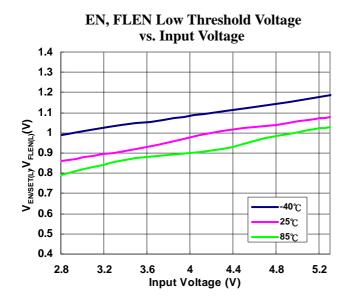

EN, FLEN High Threshold Voltage vs. Input Voltage

# **Typical Operating Characteristics (Continued)**

THITE CON

#### 一级代理:深圳市四海恒通科技有限公司 Tel: 0755-8398 3377 / 135 9011 2223 http://www.gofotech.com

# Application Information

The EUP2471 is a boost converter with a regulated output current which designed to drive high current white LEDs used in camera flash applications. The maximum flash current is set by an external resistor,  $R_{SET}$ , which sets the flash current and the maximum movie-mode current. The maximum movie-mode current is equal to the maximum programmed flash current devide the programmed flash-to-movie-mode ratio whose default value is 6.1.

A flash pulse is initiated by strobe the FLEN input pin low-to-high, which initiates a flash pulse and also starts the internal timer. The maximum flash current in the EUP2471 is set by an external resistor,  $R_{SET}$ , which sets the flash current and the maximum movie-mode current reduced by a factor of 2. The flash timer will terminate the flash current regardless of the status of the FLEN pin. This can be either used as a simple flash timing pulse or can be used as a safety timer in the event of a control logic malfunction to prevent the LED from over-heating.

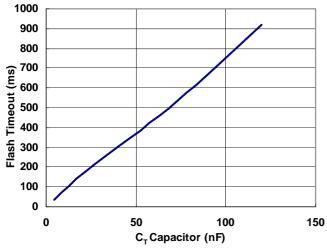

The maximum flash time is determined by an external timing capacitor connected to the  $C_T$  pin. The flash duration can be set from 50ms up to a maximum of 1s which determined by customer. The I<sup>2</sup>C-compliant interface allows further adjustment of the flash timer duration. This allows the flash timer duration to be reduced in 16 linear steps from the maximum time set by the timing capacitor. If the safety timer is not needed in the application, it can be disabled by connecting the  $C_T$  pin directly to AGND.

The EUP2471 has two LED current sources which share the output current equally. For a single white LED application, the two current sources can be connected together to apply full output current into the LED. In two LED applications, each diode can be connected to its corresponding current source (FLOUTA or FLOUTB) and the output current will be shared. In applications where only one LED is connected to either FLOUTA or FLOUTB, the unused current sink must be directly connected to OUT, thereby disable that channel.

#### Movie Mode

The movie mode current level, the flash safety timer, the output channel enable, and the flash-to-movie mode current ratio can be set through the EUP2471's I<sup>2</sup>Ccompliant interface. The movie-mode current level can be adjusted in 16 steps using a logarithmic scale where each code is 1dB below the previous code. The flash safety delay can be reduced from the maximum value programmed externally by C<sub>T</sub> in 16 linear steps. The flash current outputs FLOUTA and FLOUTB can be enabled or disabled individually or together. The flash-to-movie-mode current ratio can be set from 1:2 to 1:17 with respect to the maximum programmed flash current. The FLEN signal takes priority over movie-mode operation. Lastly, the EN pin must be toggled low-tohigh to enable the EUP2471 to accept  $I^2C$  programming instructions.

#### **Over-Temperature Protection**

Thermal protection disables the EUP2471 when internal power dissipation becomes excessive, as it disables both MOSFETs. The junction over-temperature threshold is 140°C with 15°C of temperature hysteresis. The output voltage automatically recovers when the overtemperature fault condition is removed.

#### Over-Voltage Protection (Open LED, Open Circuit)

The EUP2471's output voltage is limited by internal over voltage protection circuitry, which prevents damage to the EUP2471 from open LED or open circuit conditions. During an open circuit, the output voltage rises and reaches 5.5V (typical), and the OVP circuit disables the switching, preventing the output voltage from rising higher. Once the open circuit condition is removed, switching will resume. The controller will return to normal operation and maintain an average output voltage.

#### LED Selection

The EUP2471 is specifically designed to drive white flash LEDs (typical forward voltage of 2.5V to 4.0V). Since the FLOUTA and FLOUTB input current sinks are matched with low voltage dependence; the LED-to-LED brightness will be matched regardless of the individual LED forward voltage ( $V_F$ ) levels.

#### **Flash Mode LED Current**

The LED current is controlled by the RSET resistor. For maximum accuracy, a 1% tolerance resistor is recommended. FLOUTA and FLOUTB can be programmed up to a maximum total flash current of 1.5A or up to 750mA per channel. FLOUTA and FLOUTB output current is matched across the programming range. A flash event is initiated by asserting the FLEN pin. A flash event is automatically terminated when FLEN is disabled or if the safety timer terminates before the FLEN pin is disabled.

The maximum flash current in each FLOUTA and FLOUTB is set by the  $R_{SET}$  resistor and can be calculated using the following equation:

$$I_{FLOUTA} = I_{FLOUTB} = \frac{81K\Omega \cdot A}{R_{SET}} = \frac{81K\Omega \cdot A}{107K\Omega} \cong 750 \text{ mA}$$

per channel

To prerent excessive power dissipation during higher flash current operation,  $R_{SET}$  values smaller than  $107 k \Omega$  are not recommended.

#### Auto-Disable Feature Movie Mode LED Current

The EUP2471 is equipped with an auto-disable feature for each LED channel. After the IC is enabled and started up, a test current of 2-3mA (typical) is forced through each sink channel. The channel will be disabled if the voltage of that particular SINK pin does not drop to a certain threshold. This feature is very convenient for disabling an unused channel or during an LED fail-short event. This small test current should be added to the set

output current in both Flash and MM conditions. The maximum movie-mode current level is set by the maximum programmed flash current reduced by the programmed flash-to-movie-mode ratio in which the default value is 6.1:

$$I_{\text{MOVIE}-\text{MODE}[A/B]} = \frac{I_{\text{FLOUT}[A/B](\text{MAX})}}{6.1} = \frac{750 \text{ mA}}{6.1} \cong 120 \text{ mA}$$

To change the configuration or the settings, the EUP2471 can be programmed via the  $I^2C$  interface. Triggering the FLEN low to high will enable a flash event with the maximum flash current set by the R<sub>SET</sub> resistor or with programmed flash current set via the  $I^2C$  interface. Concurrently, the flash timer is also initiated. All data and register contents are cleared (reset to the default value) after each flash event.

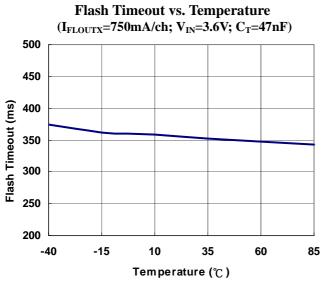

#### **Flash Safety Timeout**

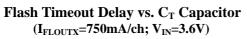

The EUP2471 includes a timer circuit that enables the flash current for a programmed period of time. This feature eliminates the need for an external, housekeeping baseband controller to contain a safety delay routine. It also serves as a protection feature to minimize thermal issues with the flash LEDs in the event an external controller's flash software routine experiences hang-up or freeze. The flash safety timeout, T can be calculated by the following equation:

$$T=7.98 s/\mu F\cdot C_T$$

Where T is in seconds and  $C_T$  is the capacitance of the timer capacitor in  $\mu F$ .

For example, using a 47nF capacitor for  $C_T$  sets the flash timeout to:

Flash Safety Timeout =  $7.98s/\mu F \cdot 0.047\mu F = 375ms$

The relationship between the flash safety timeout and the capacitance of the timer capacitor is illustrated in Flash Timeout Delay VS  $C_T$  Capacitance.

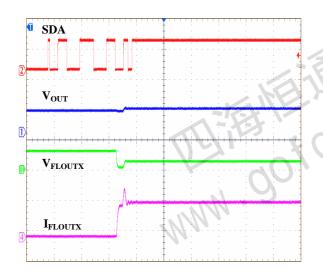

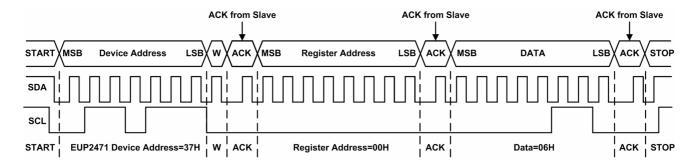

# I<sup>2</sup>C Serial Interface

The EUP2471 is fully compliant with the industry-standard I<sup>2</sup>C interface. The I<sup>2</sup>C two-wire communications bus consists of SDA and SCL lines. SDA provides data, while SCL provides clock synchronization with speed up to 400kHz. SDA data transfers device address followed by a register address and data bits sequence. When using the I<sup>2</sup>C interface, EN is pulled high to enable the device or low to disable the device. The I<sup>2</sup>C serial interface requires a master to initiate all the communications with target devices. The EUP2471 is a target device and only supports the write protocol. The EUP2471 is manufactured with a target device address of 0×37 (Hex). See Figure 3 for the I<sup>2</sup>C interface diagram.

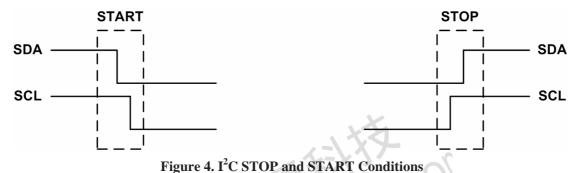

#### I<sup>2</sup>C START and STOP Conditions

START and STOP conditions are always generated by the master. Prior to initiating a START, both the SDA and SCL pins are in idle mode (idle mode is when there is no activity on the bus and SDA and SCL are pulled high by the external pull-up resistors). A START condition occurs when the master strobes the SDA line low and after a short period strobes the SCL line low. A START condition acts as a signal to all ICs that transmission activity is about to occur on the I<sup>2</sup>C bus. A STOP condition, as shown in Figure 4, is when master releases the bus and SCL changes from low to high followed by SDA low-to- high transition. The master does not issue an ACKNOWLEDGE and releases the SCL and SDA pins.

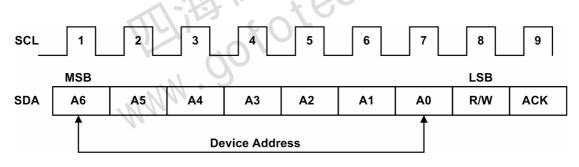

# I<sup>2</sup>C Address Bit Map

Figure5 illustrates the address bit transfer. The 7-bit address is transferred with the Most Significant Bit (MSB) first and is valid when SCL is high. This is followed by the R/W bit in the Least Significant Bit (LSB) location. The R/W bit on the eighth bit determines the direction of the transfer (a '1' for read or a '0' for write). The EUP2471 is a write-only device and the R/W bit must be set low. The Acknowledge bit (ACK) is set to low by the EUP2471 to acknowledge receipt of the address.

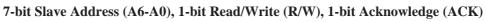

# I<sup>2</sup>C Register Address/Data Bit Map

Figure 6 illustrates the Register Address or the serial data bit transfer. The 8-bit data is always transferred most significant bit first and is valid when SCL is high. The Acknowledge bit (ACK) is set low by the EUP2471 to acknowledge receipt of the register address or the data.

# I<sup>2</sup>C Acknowledge Bit (ACK)

The Acknowledge bit is the ninth bit of each transfer on the SDA line. It is used to send back a confirmation to the master that the data has been received properly by the target device. For each ACK to take place, the master must first release the SDA line, and then the target device will pull the SDA line low, as shown in Figures 3, 5, and 6.

**Figure 3.** I<sup>2</sup>C Interface Diagram

START: A High "1" to Low "0" Transition on the SDA Line While SCL is High "1" STOP: A Low "0" to High "1" Transition on the SDA Line While SCL is High "1"

Figure 5. I<sup>2</sup>C Address Bit Map

Figure 6. I<sup>2</sup>C Register Address and Data Bit Map 8-bit Data (D7-D0), 1-bit Acknowledge (ACK)

#### **Device Register Information**

To program the register through the I<sup>2</sup>C interface, the master needs to send the EUP2471's device address,  $0 \times 37$  (Hex), first, and then sends an 8-bit register address and 8-bit data. The EUP2471 has two registers, Register 0 and Register 1. If no instruction is written to the register, the default value is applied.

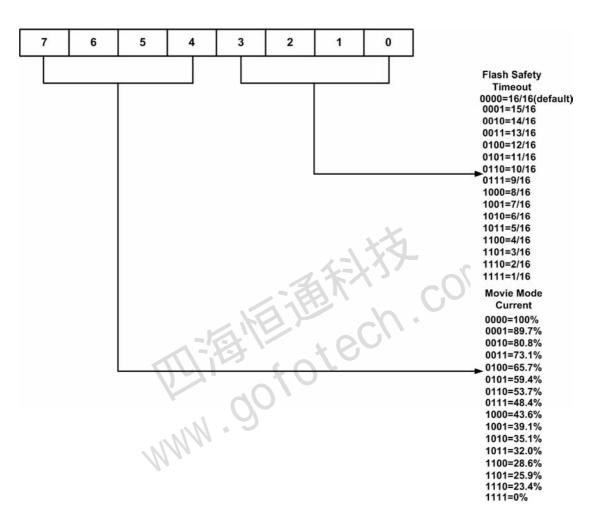

#### Register 0 (REG0), Register Address: 00h

Bits [7:4] Program the movie-mode current with 16 different percentage levels. Bits [3:0] Program the flash safety timeout with 16 different fractions from the hardware configuration,  $C_T$ .

Figure 7: EUP2471 Register 0 Programming.

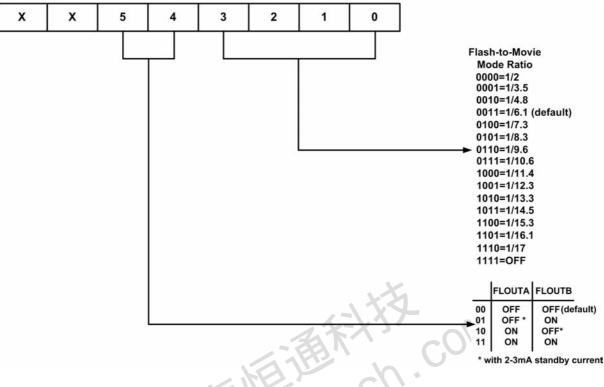

#### Register 1 (REG1); Register Address: 01h

Bits [5:4] Program the FLOUTA and FLOUTB with four ON/OFF configurations.

Bits [3:0] Program the flash-to-movie mode ratio with 16 different fractions from the hardware configuration, R<sub>SET</sub>.

# Figure 8: EUP2471 Register 1 Programming.

#### Selecting the Boost Inductor

The EUP2471 controller utilizes PWM control and the switching frequency is fixed. To maintain 2MHz maximum switching frequency and stable operation, a Manufacturer's inductor is recommended. 1µH specifications list both the inductor DC current rating, which is a thermal limitation, and peak inductor current rating, which is deter-mined by the saturation characteristics. Measurements at full load and high ambient temperature should be per- formed to ensure that the inductor does not saturate or exhibit excessive temperature rise.

The inductor (L) is selected to avoid saturation at minimum input voltage and maximum output load conditions. Worst case peak current occurs at minimum input voltage (maximum duty cycle) and maximum load. Bench measurements are recommended to confirm actual IPEAK and to ensure that the inductor does not saturate at maximum LED current and minimum input supply voltage. The RMS current flowing through the boost inductor is equal to the DC plus AC ripple components. Under worst case RMS conditions, the current waveform is critically continuous. The resulting RMS calculation yields worst case inductor loss. The RMS current value should be compared against the inductor manufacturer's temperature rise, or thermal derating guidelines:

$$I_{RMS} = \frac{I_{PEAK}}{\sqrt{3}}$$

For a given inductor type, smaller inductor size leads to an increase in DCR winding resistance and, in most cases, increased thermal impedance. Winding resistance degrades boost converter efficiency and increases the inductor's operating temperature:

#### PLOSS(INDUCTOR)= I2RMS·DCR

#### **Selecting the Boost Capacitors**

In general, it is good design practice to place a decoupling capacitor (input capacitor) between the IN and GND pins. An input capacitor in the range of 2.2µF to 10µF is recommended. A larger input capacitor in this application may be required for stability, transient response, or ripple performance. The high output ripple inherent in the boost converter necessitates the use of low impedance output filtering. Multi-layer ceramic (MLC)capacitors provide small size and adequate capacitance, low parasitic equivalent series resistance (ESR) and equivalent series inductance (ESL), and are well suited for use with the EUP2471 boost regulator. MLC capacitors of type X7R or X5R are recommended to ensure good capacitance stability over the full operating temperature range. The output capacitor is selected to maintain the output load without significant voltage droop ( $\Delta$ VOUT) during the power switch ON interval. A 2.2µF ceramic output capacitor is recommended. Typically, 6.3V or 10V rated capacitors are required for this flash LED boost output. Ceramic capacitors selected as small as 0603 are available which

meet these requirements. MLC capacitors exhibit significant capacitance reduction with applied voltage. Output ripple measurements should confirm that output voltage droop and operating stability are within acceptable limits. Voltage derating can minimize this factor, but results may vary with package size and among specific manufacturers. To maintain stable operation at full load, the output capacitor should be selected to maintain  $\Delta$ VOUT between 100mV and 200mV. The boost converter input current flows during both ON and OFF switching intervals. The input ripple current is less than the output ripple and, as a result, less input capacitance is required.

#### **PCB Layout Guidelines**

Boost converter performance can be adversely affected by poor layout. Possible impact includes high input and output voltage ripple, poor EMI performance, and reduced operating efficiency. Every attempt should be made to optimize the layout in order to minimize parasitic PCB effects (stray resistance, capacitance, and inductance) and EMI coupling from the high frequency SW node. The following PCB layout guidelines should be considered:

1. Minimize the distance from capacitor CIN and COUT's negative terminals to the PGND pins. This is especially true with output capacitor COUT, which conducts high ripple current from the output to the PGND pins.

2. Minimize the distance under the inductor between IN and switching pin SW; minimize the size of the PCB area connected to the SW pin.

3. Maintain a ground plane and connect to the IC PGND pin(s) as well as the PGND connections of CIN and COUT.

4. Consider additional PCB exposed area for the flash LEDs to maximize heat sinking capability. This may be necessary when using high current application and long flash duration application.

5. Connect the exposed paddle (bottom of the die) to either PGND or GND. Connect AGND, FLGND to GND as close as possible to the package.

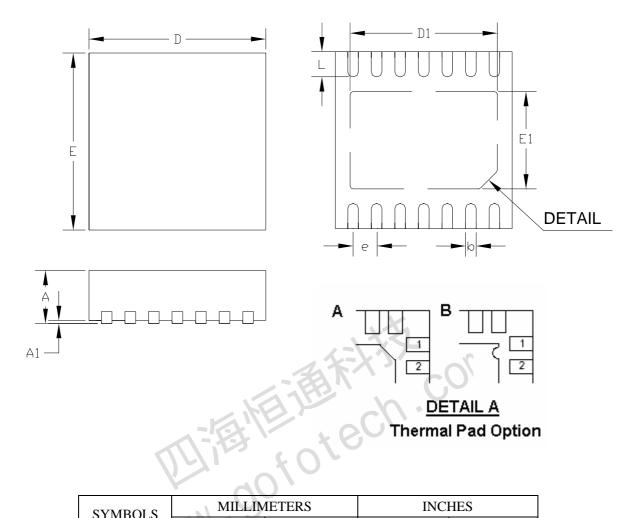

# Package Information

TDFN-14

| SYMBOLS | MILLIMETERS |      | INCHES      |       |  |  |  |

|---------|-------------|------|-------------|-------|--|--|--|

| STMDOLS | MIN.        | MAX. | MIN.        | MAX.  |  |  |  |

| A       | 0.70        | 0.80 | 0.028       | 0.031 |  |  |  |

| A1      | 0.00        | 0.05 | 0.000       | 0.002 |  |  |  |

| b       | 0.13        | 0.23 | 0.008       | 0.014 |  |  |  |

| E       | 2.90        | 3.10 | 0.114       | 0.122 |  |  |  |

| D       | 2.90        | 3.10 | 0.114       | 0.122 |  |  |  |

| D1      | 2.50        |      | 0.098       |       |  |  |  |

| E1      | 1.65        |      | 0.065       |       |  |  |  |

| e       | 0.40        |      | 0.0         | 16    |  |  |  |

| L       | 0.30        | 0.50 | 0.012 0.020 |       |  |  |  |